Schaltungstechnik digitaler Schaltkreise

Die integrierten Schaltkreise der logischen Gatter basieren auf Halbleiterschaltungen mit Transistoren als kontaktlose elektronische Schalter. Die anfangs genutzten Schalteigenschaften von Dioden sind durch bipolare und unipolare Transistoren ersetzt worden. Vom Schaltungskonzept bestimmt, ergeben sich einzelne Schaltkreisgruppen mit speziellen Eigenschaften. Die korrekte Zusammenarbeit unterschiedlicher Schaltkreisgruppen im elektrischen Schaltungsverbund ist nur mithilfe von Adapterschaltung möglich.

Unterschieden wird zwischen bipolaren Schaltkreisen, wo der Stromtransport durch Elektronen und Defektelektronen (Elektronenlöcher) mit zwei Ladungsträgerarten erfolgt. Die bekannteren Schaltkreisgruppen sind die Dioden-Transistor-Logik (DTL), Transitor- Transistor-Logik (TTL), Emitter-coupled-Logik (ECL) Schaltkreise.

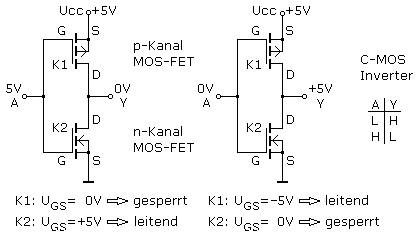

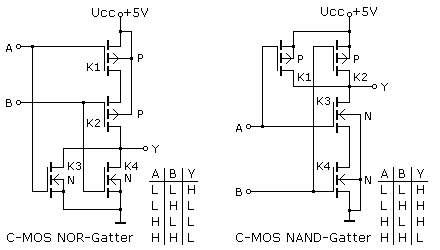

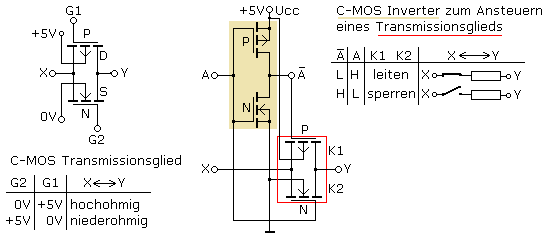

Die zweite große Gruppe basiert auf der CMOS Technik, complementary metal oxide semiconductor, und verwendet unipolare Schaltkreise. Es handelt sich um Feldeffekt-(FET)-Transistoren mit isoliertem Gate, wo nur Elektronen als einzige Ladungsträgerart beteiligt sind. Verwendet werden mit N- und P-Kanal komplementäre selbstsperrende metal oxide semiconductor Feldeffekttransistoren (MOSFET).

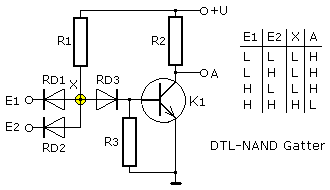

DTL-Technik

Die Gatterschaltungen, die anfangs diskret mit Dioden und Transistoren aufgebaut, dann in Dünn- und Dickschichttechnologie bis hin zu monolithischen IC-Schaltkreisen weiterentwickelt wurden, sind bedeutungslos geworden. Die einfach nachvollziehbare Arbeitsweise ist an der Standardschaltung eines UND Gatters, das mit Diodenlogik arbeitet und mit der folgenden Transistor-Inverterstufe ein NAND-Gatter in DTL-Technik ergibt, zu erkennen. Die Schaltung ist für positive Schaltlogik ausgelegt.

Liegen beide Eingänge an Masse und haben mit 0 V Low Pegel, dann leiten beide Eingangsdioden und am Knotenpunkt X stellt sich mit rund 0,7 V ebenfalls Low Pegel ein. Führt nur ein Eingang Low Pegel, dann ändert sich der Pegel am Punkt X selbst dann nicht, wenn der zweite Eingang High Pegel hätte. Mit einer nach Masse leitenden Diode bleiben am Knotenpunkt X die 0,7 V Diodenflussspannung bestehen. Der Ausgang A bleibt mit gesperrtem Transistor auf High Pegel.

Die Diode RD3 sorgt mit dem Widerstand R3 für ein sicheres Schalten des Transistors. Er kann erst durchschalten, wenn das Anodenpotenzial dieser Diode um 0,7 V höher als ihr Kathodenpotenzial ist. Dieser Zustand wird erreicht, wenn beide Eingänge an der Betriebsspannung auf High Pegel liegen. Nicht angeschlossene, offene Eingänge entsprechen einem High Pegel. Das Potenzial am Knoten X ist dann mit rund 1,4 V als High Pegel zu werten. Der Transistor wird leitend und der Ausgang A wechselt mit der verbleibenden Kollektor-Emitterrestspannung von rund 0,5 V auf Low Pegel.

Beim Pegelwechsel am Knoten X von High nach Low unterstützt der Widerstand R3 das Sperren des Transistors, da die Ladungsträger aus der Basiszone schnell nach Masse abfließen können. Die allgemeinen elektrischen Daten der DTL-Schaltkreise waren recht gut. Bei einer Betriebsspannung von 6 V liegen die Verlustleistung je Glied bei 9 mW und die Signallaufzeiten um 30 ns. Diese Schaltkreise zeichnen sich durch eine relativ hohe statische Störsicherheit von 1,2 V aus.

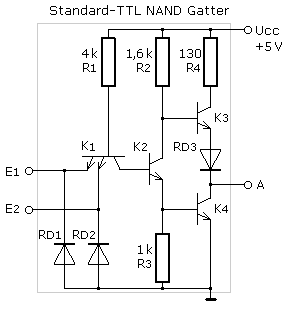

TTL-Technik

Die Eingangsdioden in der DTL-Technik wurden durch einen bipolaren Multi-Emitter-Transistor ersetzt. In dieser Weiterentwicklung zur TTL-Technik kann man die Basis-Emitterstrecken des Eingangstransistors als Diodenersatz ansehen. Diese spezielle Art der Transistoren hat den Eingängen entsprechend getrennte Basis-Emitterzonen mit herausgeführten einzeln ansteuerbaren Emittern. Die TTL-Technik gibt es nur als monolithisch integrierte Schaltungen. Das Bild zeigt das Schaltungsprinzip eines Standard-TTL NAND Gatters für positive Schaltlogik.

Für die TTL-Technik ist eine maximale Betriebsspannung von +5,5 V vorgesehen, normal sind es +5 V. Der Multi-Emitter-Transistor K1 am Eingang ist immer leitend und wird von einem durch R1 begrenzten Basisstrom durchflossen. Der Transistor arbeitet im Inversbetrieb. Da beim Umschalten die Basiszone nicht von den Ladungsträgern geräumt werden muss, ergeben sich kurze Reaktionszeiten.

Die Gegentakt-Endstufe, eine Totem-Pole-Schaltung bewirkt, dass die kurzen Schaltzeiten auch am Ausgang wirksam sind. Die niederohmige Endstufe verträgt höhere Ausgangsströme und verbessert damit die Flankensteilheit des Ausgangssignals.

Die eingetragenen Widerstandswerte entsprechen der Standard-TTL-Serie. Der Widerstand R1 ist so dimensioniert, dass der Eingangstransistor mit UB ≥ UC in die Sättigung gelangt. Die Steuerung des Multi-Emitter-Transistors erfolgt nur über die Emitter, da das Basispotenzial konstant bleibt.

Low Pegel am Eingang

Liegt mindestens einer der Emitter des Eingangstransistors mit Low Pegel an Masse, dann ist K1 bis in die Sättigung leitend durchgesteuert. Seine Kollektor-Emitterspannung liegt bei UCE ≈ 0,3 V. Der durch R1 begrenzte Basisstrom fließt als Emitterstrom aus den Eingängen heraus nach Masse ab. Parallel zur Kollektor-Emitterstrecke von K1 liegt die Reihenschaltung der Basis-Emitterstrecke des Transistors K2 mit dem Widerstand R3. Der Kollektorstrom von K1 hält das Basispotenzial des Transistors K2 niedrig und sperrt ihn.

Der gesperrte Transistor K2 zieht keinen Kollektorstrom und liefert keinen Emitterstrom. Dadurch werden die Ausgangstransistoren K3 leitend durchgeschaltet und K4 gesperrt. Das Ausgangspotenzial ist hoch und durch K3 kann ein durch R4 begrenzter großer Ausgangsstrom fließen.

High Pegel am Eingang

Sind beide Eingänge mit der Betriebsspannung verbunden und führen High Pegel, dann arbeitet der Multi-Emitter-Transistor im inversen Betrieb, wo die Funktion des Emitters mit dem Kollektor quasi vertauscht ist. Die Technologie des Multi-Emitter-Transistors sorgt für einen im Inversbetrieb weit unter 1 liegenden Stromverstärkungsfaktor. In der TTL-Technik beträgt der in den Eingang fließende Emitterstrom rund 40 μA. Der Transistor leitet auch dann, wenn beide Emitter offen bleiben. Der Basisstrom fließt als Kollektorstrom zum Transistor K2 und steuert diesen in den leitenden Zustand. Sein Emitterpotenzial lässt ab 0,7 V den Ausgangstransistor K4 leiten.

Für das Basispotenzial von K4 kann man UB0 = 0,7 V und für den durchgeschalteten Transistor K2 ein Kollektor-Emitterpotenzial von UCE ≈ 0,3 V annehmen. Das Kollektorpotenzial von K2 das gleichzeitige Basispotenzial von K3 liegt bei 1 V, wodurch der noch leitende obere Ausgangstransistor K3 nunmehr gesperrt wird. Der Widerstand R4 dient der Strombegrenzung während des Umschaltens, wo beide Ausgangstransistoren kurzzeitig leitend sein können.

Der niederohmig leitende untere Ausgangstransistor zieht den Ausgang auf seine geringe Kollektor-Emitterrestspannung UCEsat ≈ 0,3 V. Das Anodenpotenzial der Diode RD3 liegt um 0,7 V höher, wodurch der npn-Transistor K3 mit seiner UB0 = UE0 jetzt sicher gesperrt bleibt.

Die beiden nach Masse in Sperrrichtung geschalteten Eingangsdioden sollen beim Potenzialwechsel von High auf Low ein Überschwingen verhindern. Ohne Dioden könnten Spannungsspitzen bis −2 V auftreten, die von den Dioden auf maximal −0,7 V begrenzt werden.

Totem-Pole-Schaltung

Die im Gegentakt angesteuerte Ausgangsstufe arbeitet mit gleichen npn-Transistoren und ist nicht vergleichbar mit den aus der Analogtechnik bekannten Gegentaktendstufen. Sie ist der Quasikomplementärendstufe ähnlich, aber auf schnelles Umschalten optimiert. Die im englischen Sprachraum auch totem pole genannte Gegentaktschaltung würde Analogsignale stark verzerren. Sie ist sehr niederohmig und ermöglicht mit ihrem relativ hohen Ausgangsstrom ein schnelles Umladen der Kapazitäten bei angeschlossener R-C-Ausgangslast mit dem Ergebnis steiler Signalflanken.

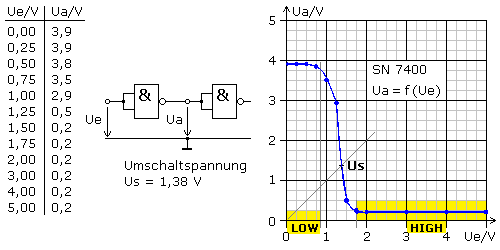

Spannungspegel und Übertragungskennlinie

Mit den Pegelbezeichnungen High und Low wird die digitale Logik einer Schaltung beschrieben. Zur Beschreibung des elektrischen Verhaltens der zugrunde liegenden Schaltung sind Spannungs- und Stromwerte notwendig. Zu jeder Schaltkreisfamilie gibt es definierte elektrische Grenzdaten, innerhalb derer die Schaltfunktionen sicher erfolgen. Die Ein- und Ausgänge der Schaltkreise sind nur begrenzt belastbar. Mit zunehmender Ausgangsbelastung nimmt der Strom zu und die Spannung ab und kann dabei einen Spannungspegel erreichen, der von angeschlossenen Gattern weder als logisches High noch Low interpretiert werden kann.

Die definierte Betriebsspannung für TTL-Schaltkreise beträgt +5 Volt. Untersucht man die Ausgangsspannung der Schaltkreise als Funktion der Eingangsspannung, so erhält man die Übertragungskennlinie. Aus ihr kann unter anderem der Spannungsbereich für ein sicheres logisches High und Low ermittelt werden. Das Bild zeigt für ein Standard-TTL NAND-Gatter die Messschaltung und die Übertragungskennlinie.

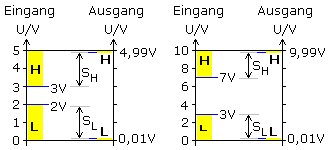

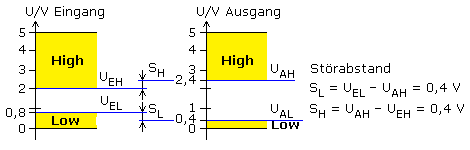

Die Umschaltspannung ist auf den Punkt festgelegt, wo in der Übertragungskurve die Eingangs- und Ausgangsspannung gleich ist. Allerdings besteht dann zwischen High und Low kein Sicherheitsabstand und kleinste Abweichungen im Bereich von Us ergeben nicht vorhersagbare Ergebnisse. Ein größerer Sicherheitsabstand ist notwendig, zumal die Übertragungskennlinie zusätzlich von der Ausgangsbelastung und der Betriebstemperatur abhängig ist. Als Sicherheitsabstand bietet sich der nichtlineare Bereich zwischen High und Low an. Die genauere Definition für Standard-TTL Schaltkreise ist der folgenden Skizze zu entnehmen. Sie zeigt den statischen Störspannungsabstand für TTL-Gatter, wobei die zeitliche Dauer der Störimpulse größer als die Ausgangsverzögerungszeit tPD (propargation delay) ist. Jeder Störabstand steht mit 0,4 V für den denkbar ungünstigsten Fall (worst case).

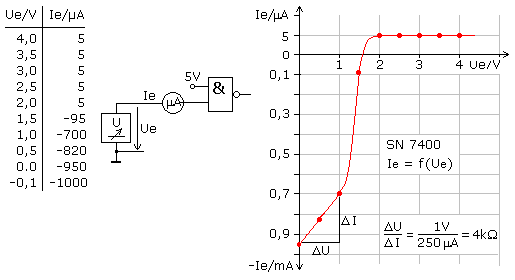

Eingangskennlinie bei Standard-TTL

Das folgende Bild zeigt die Messschaltung zur experimentellen Ermittlung der Eingangkennlinie eines Standard-TTL NAND-Gatters. Die einstellbare Eingangsspannung wurde von 4 V schrittweise bis knapp unter 0 V verringert und der sich einstellende Eingangsstrom gemessen. Oberhalb von 2 V fließt ein konstanter sehr kleiner positiver Eingangsstrom von 5 μA in den Eingang hinein. Unterhalb von 2 V beginnt der Multi-Emitter-Eingangstransistor zu leiten und der nunmehr aus dem Eingang herausfließende Strom nimmt schnell zu. Für Eingangsspannungen kleiner 1 V hat die Kennlinie eine lineare Steigung. Ihr Kehrwert entspricht mit 4 kΩ dem Wert des Basisvorwiderstands vom Eingangstransistor.

Ausgangskennlinien bei Standard-TTL

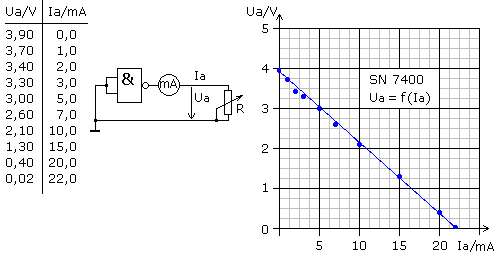

Ausgehend vom High oder Low Zustand am Ausgang gibt es zwei Ausgangskennlinien. Die Kennlinie stellt die Funktion Ua = f(Ia) dar und ist von der Ausgangsbelastung und der Temperatur abhängig. Das folgende Bild zeigt die Messschaltung und die damit erstellte Ausgangskennlinie für den High Zustand eines Standard-TTL NAND-Gatter.

Mit zunehmender Belastung nimmt die Ausgangsspannung linear ab. Der Absolutwert der Kurvensteigung errechnet sich zu rund 170 Ohm. Er setzt sich aus der Reihenschaltung R4, dem RCE des leitenden Transistors K3 und dem Durchlasswiderstand der Diode RD3 in der Ausgangsschaltung des Gatters zusammen.

In der TTL-Serie ist eine minimale Ausgangsspannung von 2,4 V für den High Zustand festgelegt. Der Ausgang könnte also mit maximal 7 mA belastet werden. Dieser Wert wird auch beim Anschluss normal vieler TTL-Eingänge nicht erreicht.

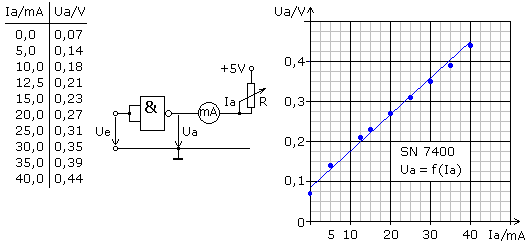

Das folgende Bild zeigt die Messschaltung und die damit erstellte Ausgangskennlinie für den Low Zustand des TTL-Gatters. Beide parallel geschalteten Eingänge liegen mit 4 V auf High. In den Ausgang wird ein definierter Strom eingespeist und die sich einstellende Ausgangsspannung des Gatters gemessen. Mit zunehmendem Strom nimmt die Ausgangsspannung linear zu. Aus der Steigung ermittelt sich der Widerstandswert zu rund 9Ω. Der Wert gehört zum Bahnwiderstand RCE des leitenden Ausgangstransistors K4.

In der TTL-Serie ist eine maximale Ausgangsspannung von 0,4 V als Low Zustand festgelegt. Das Gatter kann somit rund 32 mA aufnehmen. Aus einem TTL-Gatter könnten im 'worst case' Fall im Low Zustand 1,6 mA fließen und belasten damit den steuernden Ausgang des vorgeschalteten Gatters. Der Ausgang eines TTL-Gatters könnte im Low Zustand maximal 20 TTL-Eingänge steuern.

Eingangslastfaktor – Fan-in

Jeder Gattereingang belastet einen angeschlossenen Gatterausgang. Der Eingangslastfaktor oder Fan-in hat den Wert 1, wenn er der Belastung des Standardgatters der Schaltkreisfamilie entspricht. Der Eingangslastfaktor ist definiert als das Stromverhältnis am Eingang eines vorliegenden Schaltkreises zum Standardgatter dieser Schaltkreisfamilie. FI = Ie / Ie typ. Die festgelegten Eingangswerte der TTL-Serie sind für den Low Eingangszustand: 0,4 V und −1,6 mA und für den High Eingangszustand: 2,4 V und 40 µA. Der Eingangslastfaktor FI oder Fan-in hat den Wert 1, wenn er diese Belastung verursacht.

Ausgangslastfaktor – Fan-out

Der Ausgangslastfaktor gibt an, wie viele Eingänge mit FI = 1 mit Beachtung der Grenzdaten an den Ausgang des vorliegenden Gatters angeschlossen werden können. Der Fan-out ist definiert als FQ = Ia / Ie typ. Die Anzahl n der Gatter errechnet sich aus dem Verhältnis der Lastfaktoren: n = FQ / FI.

Die Ausgangslastfaktoren eines Gatters sind für Low und High Pegel meistens unterschiedlich. Bestimmend ist der kleinere Wert. Für Standard-TTL wird allgemein ein Ausgangslastfaktor von 10 angegeben.

Schottky-TTL-Technik

In der TTL-Technik befinden sich die leitenden Transistoren im Zustand der Übersteuerung. Das Umschalten in den Sperrzustand kann erst erfolgen, wenn der Ladungsträgerüberschuss aus dem pn-Übergang abgeflossen ist. Das wirkt sich negativ auf die Schaltzeit aus.

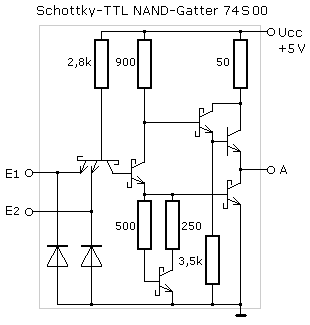

Wird bei einem übersteuerten Transistor der Basis-Kollektorstrecke eine Schottky-Diode parallel geschaltet, dann gelangt er noch in den Sättigungsbereich, wird aber nicht mehr übersteuert. Diode und Transistor liegen als Schottky-Transistor mit eigenem Schaltzeichen in integrierter Form im Schaltkreis vor. Das Bild zeigt nach einem Datenblatt der Firma Texas Instrument das mit Schottky-Transistoren integrierte NAND-Gatter 74S00.

Mit der Schottky-Technik verringert sich die Signallaufzeit von typisch 10 ns bei TTL auf rund 3 ns. Die internen Widerstände haben kleinere Werte mit dem Nachteil einer doppelt so hohe Leistungsaufnahme von 20 mW im Vergleich zu TTL mit 10 mW.

Low-Power-Schottky-TTL

Die Schottky-Technik wurde zur Low-Power Schottky-Technik weiterentwickelt und hat die Standard-TTL Gatter ersetzt. Die erweiterte Innenschaltung ist hochohmiger ausgelegt, wodurch die Signallaufzeiten mit 10 ns wieder den Standard-Gattern entsprechen. Der Leistungsbedarf mit 2 mW pro Gatter hat sich auf 20% verringert.

Durch eine verbesserte und dichtere Chiptechnologie konnten parasitäre Schaltkapazitäten minimiert werden. Das ergab kleiner Signallaufzeiten und eine nochmalige Verringerung des Leistungsbedarfs. Diese Schaltkreise gehören der ALS-TTL-Serie, in advanced-low-power-Schottky-Technik an.

TTL-Ausgangsschaltungen

Die Ausgangseigenschaften eines TTL-Gatters werden von der Innenschaltung bestimmt. Man unterscheidet zwischen dem Totem-Pole- oder Gegentakt-, Tri-State- und Open-Collector-Ausgang. Die vorangehenden Schaltbeispiele zeigen Totem-Pole-Ausgänge mit einem leitenden und einem gesperrten Transistor. Nur in einem sehr kurzen Moment des Umschaltens könnten beide Transistoren leiten, wobei der Strom durch den mit der Betriebsspannung verbundenen Kollektorwiderstand begrenzt wird.

Totem-Pole-Ausgang

Bausteine mit diesem Gegentakt-Ausgang dürfen nicht parallel geschaltet werden. Bei unterschiedlichen Ausgangspegeln würde der Ausgang im Low Zustand den High Pegel eines parallelen Gatters dauerhaft nach Masse schalten. Dabei wird der vom Hersteller maximal erlaubte Ausgangsstrom von 16 mA überschritten. Als Strombegrenzung wirken nur der Kollektorwiderstand und der Durchlasswiderstand der Diode. Rechnet man mit (130 + 20) Ohm an 5 Volt so wäre die Endstufe mit 33 mA belastet.

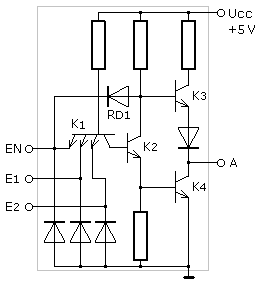

Tri-State-Ausgang

Gatter mit einem Tri-State-Ausgang arbeiten wie normale Gatter. Der Totem-Pole-Ausgang kann aber zusätzlich in den hochohmigen Zustand gesteuert werden. Dazu gibt es einen weiteren Steuereingang output enable (OE) oder nur enable (EN). Mit ihm lassen sich beide Ausgangstransistoren so sperren, dass der Ausgang sowohl zur Betriebsspannung als auch zur Masse hochohmig wird.

EN = High: Der Ausgang des NAND-Gatters wird von den Eingangspegeln an E1 und E2 normal geschaltet.

EN = Low: Die Diode RD1 leitet und legt die Kollektorspannung K2 und die Basisspannung des Transistors K3 auf 0,7 V. K3 wird gesperrt und hochohmig. Unterstützt vom normal leitenden Multi-Emitter-Transistor wird sein Kollektorpotenzial selbst bei High Pegel an E1 und E2 so niedrig, dass mit fehlender Basisansteuerung der Transistor K2 gesperrt bleibt. Folglich ist auch K4 ohne Basisansteuerung gesperrt und hochohmig.

Das Verhalten des vollkommen gesperrten Ausgangs wird als neutral bezeichnet, da er für weitere angeschlossene Gatterausgänge als nicht vorhanden erscheint. Mit der Tri-State-Technik lassen sich Ausgänge parallel an eine gemeinsame Datenleitung (BUS) schalten, wobei die Enable-Steuersignale immer nur einen Ausgang an den BUS freigeben.

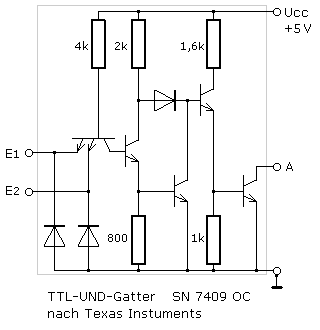

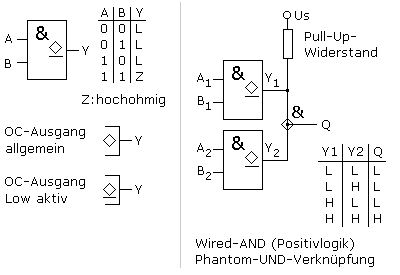

Open-Collector-Ausgang

Die Ausgangsstufe eines TTL-Glieds mit Open-Collektor-Ausgang (OC) ist ein npn-Transistor. Er wird intern an der Basis angesteuert und sein Emitter liegt an Masse. Der Kollektor ist nicht beschaltet und direkt mit dem Ausgangspin verbunden. Um als Schaltstufe zu arbeiten, muss der Ausgang über einen externen Kollektorwiderstand, dem Pull-up-Widerstand, mit einer positiven Spannungsquelle verbunden werden. Steuern die Eingangspegel die Basis-Emitterstrecke dieses Transistors in den leitenden Zustand, dann wird der Kollektorausgang niederohmig. Bei fehlender Ansteuerung oder Low Pegel an seiner Basis bleibt der OC-Ausgang hochohmig.

Im Vergleich zum Totem-Pole-Ausgang ist der Open-Collektor-Ausgang meistens höher belastbar und kann als Leistungstreiberausgang arbeiten. Der OC-Ausgang ermöglicht auch Pegelumsetzungen und Anpassungen an andere Schaltkreisfamilien, da der Pull-up-Widerstand mit einer beliebigen positiven Spannungsquelle verbunden sein kann.

Werden Open-Collector-Ausgänge parallel geschaltet, dann bestimmt der niederohmige Ausgang den Schaltzustand am Verknüpfungspunkt. Das direkte Zusammenschalten von zwei OC-Ausgängen, wo bei positiver Schaltlogik der Low Pegel dominierend und somit der Ausgang niederohmig gegen Masse ist, wirkt wie ein UND Gatter. Es wird als verdrahtetes UND (Wired-AND) bezeichnet und bildet eine logische Phantomverknüpfung. Mit einem nachgeschalteten Inverter wird aus dem Phantom-UND ein Phantom-ODER. Vorteile der Phantomverknüpfungen sind die Ersparnis an Gattern und das Fehlen von Signallaufzeiten.

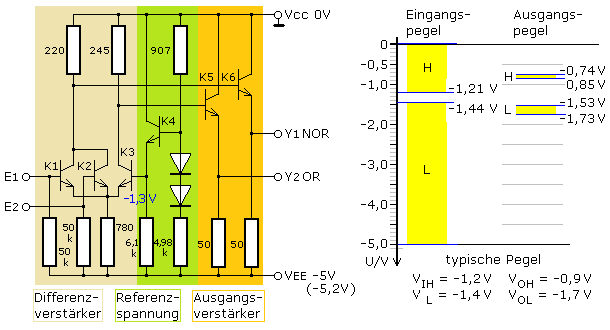

ECL-Technik

Zur weniger bekannten, aber interessanten Schaltungstechnik mit bipolaren Transistoren zählt die ECL-Schaltungstechnik, emitter coupled logic. Die Grundschaltung ist ein Differenzverstärker. Jeder Gattereingang steuert die Basis eines Transistorzweigs an. An der Basis des zweiten Transistorzweigs liegt eine Referenzspannung. Die Emitter der Zweige sind miteinander an einen gemeinsamen Widerstand, seltener an eine Konstantstromquelle gekoppelt. Das Standardgatter ist ein kombiniertes OR/NOR.

Der Differenzverstärker verstärkt die Spannungsdifferenz oder die Basisstromunterschiede, die sich zwischen dem Referenzwert und dem Eingangspegel ergeben. Die dadurch an den Kollektor-Arbeitswiderständen auftretenden Spannungen werden von bipolaren Transistorausgangsstufen in Kollektorschaltung (Emitterfolgerschaltung) ausgewertet und bilden die Ausgangspegel.

Hat mindestens einer der Eingänge mit −0,9 V High-Pegel, dann leitet K1 und/oder K2 im linken Zweig des Differenzverstärkers besser. Da der Emitterstrom konstant bleibt, wird im gleichen Maß der Strom durch den Transistor K3 geringer und der Transistor mehr gesperrt. Die Basisspannung für den Transistor K6 des invertierenden Ausgangs NOR wird negativer. Der Transistor leitet weniger Strom und wird mehr gesperrt. Das NOR-Ausgangspotenzial wird negativer und wechselt in den Low Zustand. Gleichzeitig wird die Basisspannung für den Transistor K5 des nicht invertierenden Ausgangs OR positiver. Der Transistor leitet mehr Strom und sein Emitterpotenzial wird positiver. Das OR-Ausgangspotenzial wird positiver und wechselt in den High Zustand. Nur wenn beide Eingänge Low Pegel haben, kehren sich die Stromverhältnisse im Differenzverstärker um. Der Transistor K3 leitet besser, die Basisspannung von K5 wird negativer und die von K6 entsprechend positiver. Der invertierende Ausgang NOR wechselt in den High Bereich und der nicht invertierende Ausgang OR in den Low Bereich.

In weiter optimierten ECL-Schaltungen ist der gemeinsame 780 Ω Emitterwiderstand des Differenzverstärkers durch eine Transistor Konstantstromquelle ersetzt. Die mittlere Transistorschaltung erzeugt im Vergleich zum einfachen ohmschen Spannungsteiler eine stabilere Referenzspannung. Die Dioden sorgen für einen temperaturstabilisierten Referenzwert, der zu den Eingangspegeln mittig berechnet ist. Von den Basiswiderständen unterstützt haben nicht angesteuerte Eingänge den Logikzustand Low. Der Arbeitswiderstand der Ausgangsstufe ist niederohmig ausgelegt, um die bei sehr hohen Arbeitsfrequenzen möglichen Reflexionen zwischen den im Schaltungsverbund arbeitenden Gattern zu minimieren.

Die Transistoren arbeiten als Verstärker, die sich weder im gesättigten noch übersteuerten Zustand befinden. Mit der ECL-Technik lassen sich mit über 250 MHz die höchsten Schaltfrequenzen und mit ≤1 ns extrem kurze Signallaufzeiten erreichen. Von Nachteil ist ein mit >50 mW erhöhter Leistungsbedarf. Die Standard ECL-Technik arbeitet mit der negativen Betriebsspannung von −5 Volt. Der typische Störabstand ist mit 0,3 V gering. Sollen die kurzen Schaltzeiten voll ausgenutzt werden, dann muss das Schaltungslayout den Regeln der Hochfrequenztechnik entsprechen. Signalreflexe auf längeren Leitungen sollten vermieden werden und eine Abschirmung gegen elektrische Felder ist vorteilhaft. Schaltglieder in ECL-Technik werden auch für positive Betriebsspannung 5 V, seltener 3 V hergestellt. Sie werden als PECL-Glieder, positive ECL-Glieder bezeichnet und haben einen vergleichbaren Schaltungsaufbau.