Direkt gesteuerte Flipflops

Bistabile Kippstufen, Flipflops (FF) genannt, werden durch eine geeignete Eingangssteuerung in jeweils einen ihrer beiden stabilen Zustände umgeschaltet. Mit der Eigenschaft einen logischen Zustand zu speichern, haben sie die Funktion eines 1-Bit-Speichers. In ihrer einfachsten Bauform haben sie zwei Eingänge und zwei Ausgänge. Der Eingang E1 ist der Setzeingang S und E2 der Rücksetzeingang R. Beide haben statisches Verhalten und reagieren auf logische Zustände. Für ein reproduzierbares, korrektes Schaltverhalten müssen beide Ausgänge immer entgegengesetzte logische Zustände haben. Die Eingänge werden nacheinander einzeln durch einen direkten Zustandswechsel von High zu Low oder umgekehrt angesteuert. Diese auch als asynchrone Flipflops bezeichnete Speichergruppe hat das folgende definierte Schaltverhalten:

- Setzvorgang – S

- (E1 = 1) ∧ (E2 = 0) ⇒ Q1 = 1 und folglich Q2 = 0

- Rücksetzvorgang – R

- (E1 = 0) ∧ (E2 = 1) ⇒ Q1 = 0 und folglich Q2 = 1

- Speicherzustand

- (E1 = 0) ∧ (E2 = 0) ⇒ Q1 und Q2 bleiben unverändert.

Der transistorisierte Aufbau und die Arbeitsweise bistabiler Kippstufen ist bei den Analogverstärkern eingehender beschrieben worden. In der Digitaltechnik werden Flipflop-Schaltungen mit rückgekoppelten TTL- oder CMOS-Gattern aufgebaut. Die Schaltungen benötigen die gleiche Betriebsspannung und ihre Signalpegel sind zueinander kompatibel. Die einfachen zustandsgesteuerten Flipflops sind als integrierte Schaltkreise in der TTL 74xxx-Serie nicht erhältlich. Entsprechend ihrer Funktion werden sie aus Standard NAND- oder NOR-Gatter aufgebaut.

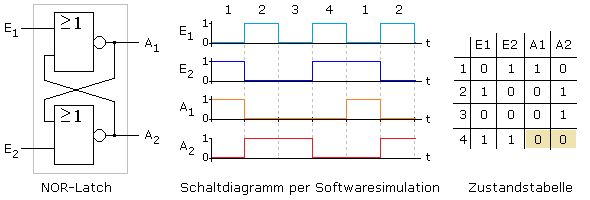

NOR-Latch

Zwei Standard NOR-Gatter mit zwei Eingängen bilden ein NOR-Flipflop oder NOR-Latch. Die englische Bezeichnung Latch, übersetzt als Riegel, beschreibt die Eigenschaft einen Eingangszustand zu speichern. Das Ausgangssignal eines jeden Gatters steuert einen Eingang des anderen Gatters, wobei der Schaltung zwei frei nutzbare Ein- und Ausgänge verbleiben. Die Grafik zeigt links das Blockschaltsymbol eines binären Flipflop-Speichers mit NOR-Gatter. Das Zeitablaufdiagramm ist das Ergebnis einer Schaltungssimulation. Die Ansteuerung erfolgte mit zwei Rechteckgeneratoren mit Frequenzen von 5 Hz und 10 Hz. Die Zustandstabelle ist aus dem Schaltdiagramm erstellt. Durch die Rückkopplungen bestimmt der Ausgangszustand eines NOR-Gatters den einen Eingangszustand seines Partners.

Die drei ersten Fälle erfüllen die Forderung nach entgegengesetzten Ausgangszuständen des Flipflops. Der 4. Fall sollte vermieden werden, ist aber in analogen Schaltungen und solchen mit digitalen Gattern problemlos möglich. Beide Ausgänge wechseln dabei in den gleichen Zustand, wie es das Zeitdiagramm für die dargestellte Schaltung mit Q1 = Q2 = 0 zeigt. Das widerspricht dem definierten Schaltverhalten des Flipflops. Wenn in Hardwareschaltungen anschließend beide Eingänge gleichzeitig zum logischen Low wechseln, dann stellt sich bedingt durch Bauteil- und Betriebstoleranzen kein reproduzierbarer Ausgangszustand mehr ein. Diese Eingangskombination ist daher unbedingt zu vermeiden. In Simulationsprogrammen, wo gleiche Baugruppen vollkommen identisch sind, stoppt der Programmablauf oder wechselt in einen für die Gatter falschen Zustand.

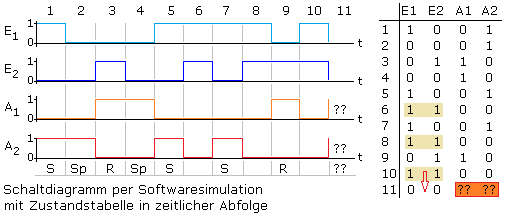

Die Simulation wurde so geändert, dass auch die zu vermeidenden Eingangskombinationen untersucht werden konnten. Das NOR-Latch setzt mit E1 = 1 den Ausgang A2 = 1 auf High und mit E2 = 1 erfolgt das Zurücksetzen (R). Beide Eingänge auf Low Pegel speichern (Sp) den vorherigen Zustand. Das folgende Schaltdiagramm zeigt das Ergebnis.

- Das NOR-Latch startet mit gesetztem Zustand: S. Die Ausgänge haben entgegengesetzte Pegel.

- Zustandswechsel nur bei E1 = 0: Die Ausgangszustände bleiben unverändert gespeichert: Sp

- Zustandswechsel nur bei E2 = 1: Beide Ausgänge wechseln in entgegengesetzte Pegel: R

- Zustandswechsel nur bei E2 = 0: Die Ausgangszustände bleiben unverändert gespeichert: Sp

- Mit E1 = 1 wird der Speichervorgang erneut ausgeführt: S. Fall 5 ist mit Fall 1 identisch.

- Zusätzlich zu E1 = 1 wird auch E2 = 1 gesetzt. Nur der Ausgang A2 wechselt seinen Pegel auf A2 = 0.

Gleiche Ausgangszustände entsprechen nicht den genormten Vereinbarungen für Flipflops. - Es wird E2 = 0 gesetzt und E1 = 1 bleibt erhalten. Das NOR-Latch wechselt in den regulären Setz-Zustand: S.

Fall 7 ist mit Fall 1 und 5 identisch. - Mit E2 = 1 und unverändertem E1 = 1 wird erneut der Fall 6 eingestellt.

- Es wird E1 = 0 gesetzt und E2 = 1 bleibt erhalten. Das NOR-Latch wird regulär zurück gesetzt: R

Der Fall 9 ist identisch mit Fall 3. - Mit E1 = 1 zum unveränderten E2 = 1 wird erneut der Fall 6 oder Fall 8 eingestellt.

- Beide Eingänge werden gleichzeitig auf Low-Pegel geschaltet. Die Simulation blockiert sich.

Erst nach dem Umschalten in den Set- oder Reset-Zustand würde sie korrekt weiter arbeiten.

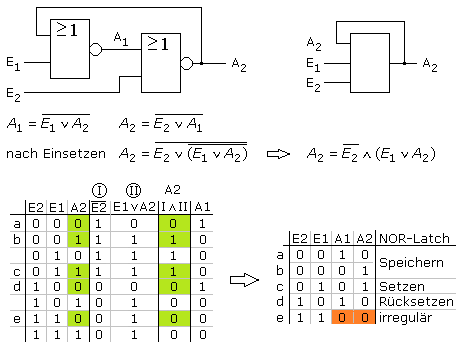

Die Wahrheitstabelle für das NOR-Latch

Die Schaltung des NOR-Latch kann umgezeichnet werden, um mithilfe der booleschen Gleichungen für den Ausgang A2 die Wahrheitstabelle zu erstellen. Es entsteht ein Funktionsblock mit drei Eingangsvariablen mit 8 unterschiedlichen Pegelkombinationen. Ein Eingangspegel ist das zurückgekoppelte Ausgangssignal A2, das auf beiden Seiten des Gleichheitszeichens steht und nur 1 oder 0 sein kann. Elektrisch und mathematisch gültig sind nur die grün hervorgehobenen Kombinationen a bis e.

Mit dem Anlegen der Betriebsspannung stellt sich entweder der Zustand (a) oder (b) ein. Die Pegeländerung auf E1 = 1 wie in (c) setzt den Ausgang auf A2 = 1. Bei weiteren nur an E1 ausgeführten Pegeländerungen bleibt der Ausgangszustand entsprechend (b) gespeichert. Wird wie in (d) nur der Eingang E2 = 1 gesetzt, dann erfolgt mit A2 = 0 ein Zurücksetzen. Wird nachfolgend nur der Pegel an E2 geändert, so bleibt dieser Ausgangszustand wie bei (a) gespeichert. Für diese vier Fälle ist die Vereinbarung nach einem entgegengesetzten Zustand für die Ausgangsvariablen A1 und A2 erfüllt.

Zu vermeidende Eingangskombination

Erhalten wie in der letzten Tabellenzeile (e) beide Eingänge einen High Pegel, dann nehmen beide Ausgänge einen Low Pegel an. Diese Eingangskombination erfüllt die boolesche Gleichung und ist somit nicht verboten. Die Vereinbarung nach entgegengesetzten Ausgangspegeln ist nicht erfüllt, daher ist diese Eingangskombination zu vermeiden. Dieser Ausgangszustand kann beim gleichzeitigen Zurücksetzen beider Eingänge auf Low nicht gespeichert werden. Das Ergebnis hängt von der Reaktionsgeschwindigkeit realer Gatter ab. Erreicht E1 vor E2 den Low Zustand, werden zwischenzeitlich die Rücksetzbedingungen durchlaufen und A2 = 0 ist der Endzustand. Reagiert E1 langsamer als E2, so entstehen kurz die Bedingungen für den Setzvorgang mit dem Endzustand A2 = 1. Die für den Fall (e) oft zu lesende Charakterisierung 'verboten' ist nur in Bezug auf die Nichterfüllung gegensätzlicher Ausgangspegel richtig. Dieser Zustand entspricht nicht der vereinbarten Regel und ist daher irregulär.

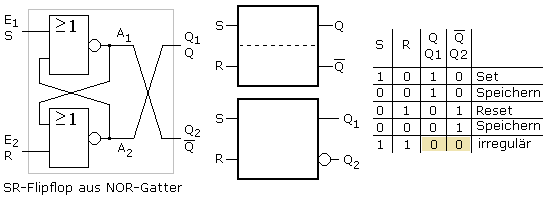

Vom NOR-Latch zum SR-Flipflop

In Anlehnung an das Normsymbol des RS-Flipflops ist das Verhalten des Eingangspegels dem gegenüberliegenden Ausgangspegel zugeordnet. Das NOR-Latch soll mit E1 = 1 gesetzt werden (S). Mit E2 = 1 wird das Zurücksetzen (R) veranlasst. Mit beiden Eingängen auf Low Pegel erfolgt das Speichern (Sp) des vorherigen Zustands. Die Ausgänge des NOR-Latch sind beim SR-Flipflop gegeneinander getauscht, sodass aus A2 = Q und A1 = ¬Q oder Q2 wird.

Bei Blocksymbolen ohne Mittellinie (aktuelle Darstellungsform) ist der untere Ausgang mit dem Negationskreis zu kennzeichnen. Der Videoclip zeigt die Arbeitsweise eines aus NOR-Gattern aufgebauten RS-Flipflops. Beim Versuch beide Eingänge aus dem irregulären Zustand gleichzeitig umzuschalten ist der Folgezustand nicht vorhersagbar.