Register- und Speicherschaltungen

In digitalen Steuerprozessen und deren Datenübertragungen, mathematischen Rechenoperationen und bei der Parallel/Seriell-Umsetzung werden binäre Informationen ein- und ausgelesen, zwischengespeichert und verschoben. Register sind Zwischenspeicher und Datenpuffer zur Aufnahme und Speicherung bestimmter und begrenzter Datenmengen, die sich bei Bedarf auslesen lassen.

Schieberegister

Schieberegister sind in Serie geschaltete 1-Bit Speicher, die aus Flipflops bestehen. Mit jedem Takt geben sie eine am Eingang eingelesene Information von Speicher zu Speicher weiter. Nach n Taktimpulsen ist eine im Register stehende Information um n Stellen verschoben worden. Zum fehlerfreien seriellen Ein- und Auslesen und zur Zwischenspeicherung sind bei einem 4-Bit Datenwort mindestens vier Speicher-FF notwendig. Das Einlesen und Verschieben erfolgt taktsynchron. Mit Schieberegistern lassen sich Daten von links nach rechts oder von rechts nach links verschieben. Schieberegister gibt es als fertige ICs mit statischer Steuerung für die Schieberichtung und wählbarer serieller oder gemischt seriell-paralleler Arbeitsweise.

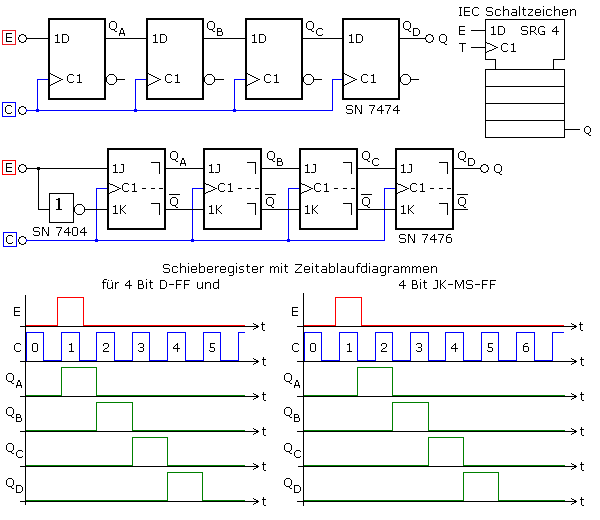

Die folgenden Schaltungen zeigen 4-Bit Schieberegister. Meistens werden D-Flipflops verwendet. Bei JK-Flipflops muss sichergestellt sein, dass die Pegel der J- und K-Eingänge entgegengesetzt sind. Es müssen JK-Master-Slave Flipflops sein, die bei jedem Takt ihre Ausgangspegel unverändert als Eingangssignal für die Folgestufe halten müssen, während sie selbst das Signal der Vorstufe einlesen.

Für Schieberegister, im englischen Sprachgebrauch shift register (SR), gibt es wie bei den Zählern IEC-Schaltzeichen mit einem Steuerblock und darunter liegendem Funktionsblock. Der serielle Dateneingang ist E. Im Bild wird zu Beginn des ersten Takts mit High Pegel der Speicher links gesetzt. Beim vierten Takt kann das Signal am seriellen Ausgang Q rechts ausgelesen werden. Das Zeitablaufdiagramm zeigt, dass die Information nach jedem Takt eine Speicherstelle nach rechts verschoben ist. Stoppt bei angelegter Betriebsspannung der Takt, so bleibt der Dateninhalt bis zur neuen Taktfreigabe gespeichert stehen.

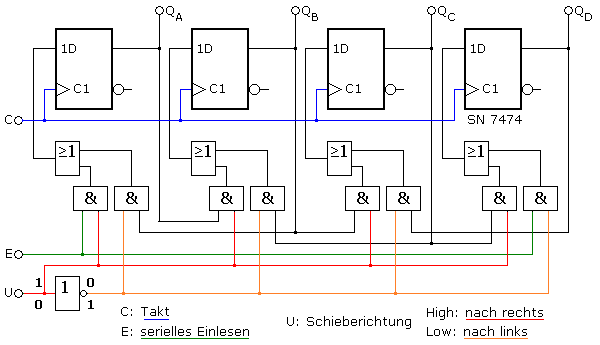

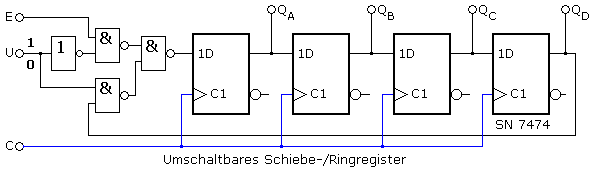

Mit einer Zusatzschaltung kann die Schieberichtung umgeschaltet werden. Um die eingelesenen Daten von rechts nach links zu schieben, sind die Ausgangssignale einer Speicherzelle an seinen Vorgänger zu geben. Bei umgekehrter Schieberichtung erfolgt das serielle Auslesen dann an der letzten linken Speicherzelle. Das Bild zeigt ein 4-Bit Schieberegister für serielles Einlesen mit wahlweiser Laufrichtung.

Mit High Pegel am U-Eingang sind alle linken UND Gatter der Gatterpaare freigeschaltet. Das Datenwort wird am linken Speicher eingelesen und das Ausgangssignal mit jedem Takt an den nachfolgenden Speicher nach rechts weitergegeben. Am QD-Ausgang werden die Daten seriell ausgelesen. Mit Low Pegel am U-Eingang sind alle rechten UND Gatter der Gatterpaare freigeschaltet. Das serielle Einlesen erfolgt am rechten Speicher. Die Ausgangssignale werden mit jedem Takt an den Eingang des vorhergehenden links stehenden Speichers weitergegeben. Das serielle Auslesen erfolgt am QA-Ausgang.

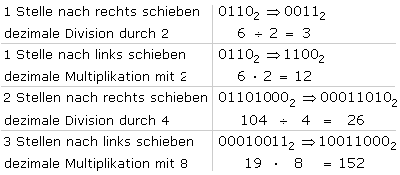

Nützlich ist das Rechts-, Linksschieben bei der Multiplikation und Division von Dezimalzahlen durch Zweierpotenzen. Wird die eingelesene Dualzahl um eine Stelle nach links geschoben, entspricht das dezimale Ergebnis der Multiplikation mit 2. Zur Division durch 2 muss die entsprechende Dualzahl um eine Stelle nach rechts geschoben werden.

Schieberegister werden auch zur Verzögerung von Signallaufzeiten eingesetzt. Das Ausgangssignal eines n-Bit Schieberegisters entspricht einem um n Takte verzögerten Eingangssignals. Sie kommen zum Beispiel in der Kommunikationstechnik und digitalen Filtern zur Anwendung.

Seriell- zu Parallelwandlung

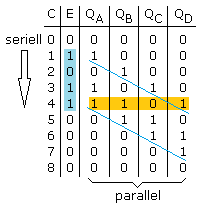

Die Funktionstabelle zeigt, dass zum kompletten seriellen Einlesen des 4-Bit Datenworts (1101), beginnend mit dem niederwertigsten Bit, vier Takte notwendig sind. Das serielle Auslesen am QD-Ausgang ist nach dem 7. Takt beendet und erfolgt nach dem FIFO-Prinzip (first in first out).

Nach dem 4. Takt kann das Datenwort auch parallel an allen Ausgängen ausgelesen werden. Der Ausgang QA gibt das MSB und QD das LSB an. Ein Schieberegister kann somit einen seriellen Datenstrom in parallele Datenworte wandeln. Zum Auslesen sollte der Takt gesperrt bleiben.

Die Parallel- zu Seriellwandlung ist ebenso machbar. Ein vor dem 1. Takt an den Parallelausgängen anliegendes Datenwort ist nach dem Takt in den Speicher komplett eingelesen. Zum seriellen Auslesen ist dann die Paralleleingabe zu verriegeln. In den folgenden Takten wird der Speicher an der letzten Speicherzelle, beim 4-Bit Speicher ist es QD, seriell ausgelesen.

Anwendung finden diese Verfahren zur seriellen Übertragung digitaler Daten. Die senderseitig abgetasteten und am Analog-Digitalwandler parallel abgenommen Datenworte werden zur Einsparung vielen Datenleitungen vor der Übertragung in einen seriellen Datenstrom gewandelt. Auf der Empfängerseite werden taktsynchron gesteuert daraus wieder parallele Datenworte gebildet. Anschließend kann die Rückwandlung durch einen Digital-Analogwandler folgen.

Ringregister

Ringregister oder Ringzähler genannt sind rückgekoppelte Schieberegister. Der Inhalt ist nach einmaligem Durchlauf nicht gelöscht und wird am Eingang wieder eingelesen, um taktgesteuert kontinuierlich im Ring herum zu wandern. Anwendungen findet man in der Ansteuerung von Laufschriftanzeigen und Schrittschaltwerken zur Drehfelderzeugung von Motoren. Eine Zusatzschaltung erlaubt die Wahl zwischen Schieberegister oder Ringzähler.

Die Schaltung arbeitet mit Low Pegel am U-Eingang als Schieberegister, da damit das serielle Einlesen vom Eingang E am oberen NAND Gatter freigeschaltet ist. Vor dem Durchlaufen des Registers muss das Eingangssignal nochmals durch ein NAND Gatter negiert werden. Die Daten verlassen taktgesteuert den seriellen QD-Ausgang.

Ein High Pegel am U-Eingang sperrt das obere NAND Gatter und gibt das untere NAND Gatter frei, sodass die an QD ausgelesenen Daten erneut in den Eingang des ersten Speichers eingelesen werden. Solange am Umschalteingang ein statischer High Pegel anliegt, durchlaufen die Daten das Register in zyklischer Folge.

Speicherregister

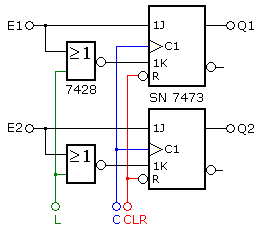

Die Register enthalten eine der Datenwortlänge entsprechende Anzahl taktgesteuerter JK-Flipflops, die einzeln gesetzt oder gelöscht werden können. Die eingelesenen und gespeicherten Datenworte werden nicht verschoben und stehen am Ausgang zur Nutzung bereit, solange die Betriebsspannung anliegt und die Lesefreigabe der Eingänge gesperrt bleibt. Haben die Flipflops einen taktunabhängigen Rückstelleingang, kann das Register schnell und einfach gelöscht werden.

Die Schaltung zweigt das Prinzip eines 2-Bit Speicherregisters, das durch Hinzufügen weiterer Speicher-FF in der Datenwortlänge erweitert werden kann. Die an den Eingängen anliegenden High oder Low Pegel werden taktsynchron eingelesen, solange an der Leseleitung mit L = 0 Low Pegel liegt. Mit L = 1 erhalten alle K-Eingänge der Flipflops Low Pegel und halten die eingelesenen Eingangszustände an ihren Ausgängen gespeichert. Mit CLR = 0 erfolgt ein unbedingtes Löschen.