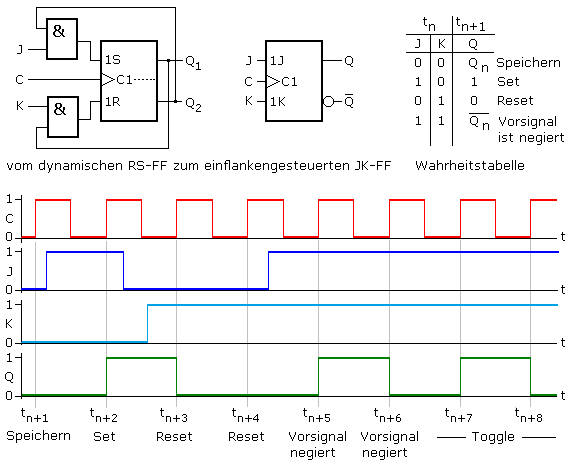

Einflankengesteuertes JK-Flipflop

Auf der Grundlage eines RS-Flipflops lassen sich viele Anwendungen verwirklichen. Für ein sicheres Schaltverhalten ist bei allen der irreguläre Eingangszustand mit dem gleichzeitigen High Pegel aller R und S Eingänge zu vermeiden. Mithilfe einer Eingangserweiterung entsteht aus dem dynamischen RS-FF ein vielseitig verwendbares einflankengesteuertes JK-FF. Der neue Speicherbaustein erfüllt wie ein RS-FF das Setzen, Rücksetzen und Speichern. Bei der irregulären Ansteuerung wird das Ausgangssignal invertiert. Das neue dynamische JK-FF verhält sich bei der Ansteuerung mit S = R = 1 wie T-FF und halbiert die Frequenz des Steuertakts. Beim Einschalten gehen die kommerziellen Einflanken JK-Flipflops zumeist in den definierten Reset-Zustand mit Q1 = 0 und Q2 = 1.

Das im Bild gezeigte Zeitablaufdiagramm ist das Ergebnis einer Simulationsschaltung für ein JK-FF. Ein aus NAND Gattern aufgebautes RS-FF wurde mit einem dynamischen Zusatz versehen und mit UND Gattern zum JK-FF erweitert.

T-Flipflop

Im Bild oben liegen die Eingänge J und K ab tn+5 auf High Pegel. Das JK-FF verhält sich wie ein T-FF. Das gleiche Verhalten entsteht, wenn die Ein- und Ausgänge gekreuzt, J mit Q2 und K mit Q1 verbunden werden. Das Ausgangssignal an Q1 (Q) hat die halbe Taktfrequenz mit einem exakten 1:1 Tastverhältnis.

Signalschaltzeiten

In der Realität vergeht beim Signalwechsel eine gewisse Zeit, die bei digitalen Rechtecksignalen sehr kurz sein kann und in den bildlichen Darstellungen nicht erkennbar oder darstellbar ist. Für den Wechsel von High nach Low kann eine Anstiegszeit tr (rise time) und entsprechend von Low nach High eine Abfallzeit tf (fall time) bestimmt werden. Zur sicheren Verarbeitung muss ein Impuls für eine endliche Zeit, der Pulsdauer oder in seiner Ausdehnung, der Pulsweite tw konstant bleiben. Alle Signale benötigen eine bestimmte Zeit, als Verzögerungszeit bezeichnet, um vom Eingang einer Schaltung an den Ausgang zu gelangen.

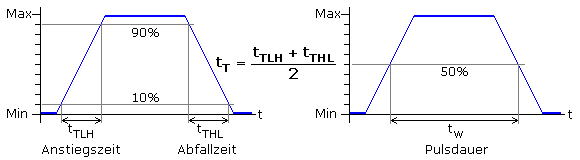

Signalübergangszeit

Sie wird aus der Anstiegszeit von Low auf High und der Abfallzeit von High auf Low bestimmt. Sie ergibt sich aus der mittleren Steilheit der Signalflanken zwischen 10% und 90% bei tTLH und zwischen 90% und 10% bei tTHL bezogen auf den jeweiligen Endwert. Die mittlere Signalübergangszeit tT errechnet sich aus dem arithmetischen Mittel der beiden Teilzeiten.

Pulsdauer – Pulsweite

Die Pulsdauer oder Pulsweite tw ist die notwendige Mindestzeit, um das Signal korrekt zu verarbeiten. Der Referenzwert liegt bei 50% der Amplitude.

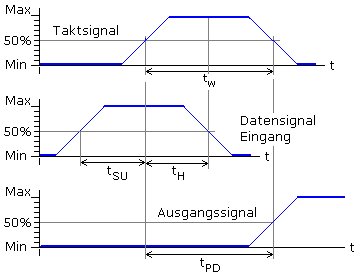

Vorbereitungs- und Haltezeit

Für einen sicheren Schaltvorgang ist es notwendig, dass die Datensignale eine bestimmte Zeit anliegen. Es ist die Vorbereitungszeit, die auch Setup time tSU genannt wird. Nach dem Erreichen des Umschaltpunkts auf der Taktflanke ist zur sicheren Auswertung noch eine minimale Haltezeit tH notwendig, in der die Pegel des Daten- und Taktsignals konstant bleiben. Nur innerhalb dieser Zeitspanne wirken sich Pegeländerungen oder Störungen aus. Die dynamisch gesteuerten Gatter der TTL-74xxx-Serie haben eine durchschnittliche Haltezeit von 5 ns.

Ausgangsverzögerungszeit

Der Referenzwert zur Bestimmung liegt bei 50% auf der Flankenmitte. Die Ausgangsverzögerungszeit oder propagation delay tPD meistens nur tP ist die Zeit, die zwischen der Signaländerung am Eingang und der entsprechenden Ausgangsänderung vergeht. Das Bild zeigt die Zeiten im Zusammenhang.

Die Zeitspanne der Pulsdauer muss mindestens der Ausgangsverzögerungszeit entsprechen. Es gilt daher: tw ≥ tPD.

Die kürzeste Schaltzeit eines Flipflops ist die Summe aus der Vorbereitungs- (setup) und Ausgangsverzögerungszeit: t ≥ tSU + tPD

Das Eingangssignal muss zur sicheren Verarbeitung mit konstantem Pegel für die Haltezeit tH anliegen. Die maximale Taktfrequenz zur korrekten Datenverarbeitung errechnet sich aus dem Kehrwert der Schaltzeit.

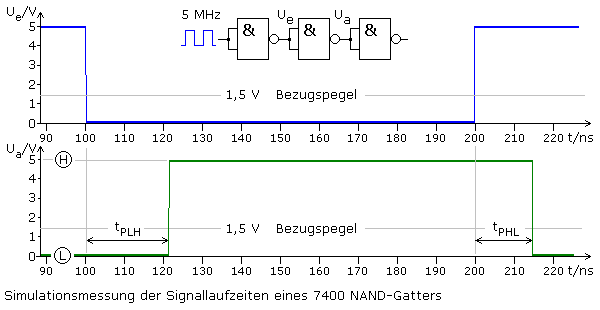

Signallaufzeit – Impulsverzögerungszeit

Für die Schaltkreise der Standard TTL-Serie gibt die Impulsverzögerungszeit tPLH die Zeitspanne an, die bei 1,5 V beim Pegelwechsel von Low auf High zwischen Eingangs- und Ausgangszustand vergeht. Die entsprechende Zeit tPHL wird bei 1,5 V beim Pegelwechsel von High auf Low zwischen Eingangs- und Ausgangszustand gemessen. Das arithmetische Mittel ist die mittlere Signallaufzeit: tp = 0,5 · (tPLH + tPHL)

Das folgende Bild zeigt die Simulationsmessung beider Signallaufzeiten für ein als Inverter geschaltetes TTL NAND-Gatter. Um dem Verhalten des Gatters im Schaltungsverbund gerecht zu werden, wird das Taktsignal von einem vorgeschalteten Gatter aufbereitet und der Ausgang durch ein weiteres Gatter belastet. Die beiden Impulsverzögerungszeiten sind stets etwas unterschiedlich. Die mittlere Signallaufzeit tp liegt bei vielen Standard TTL Schaltkreisen der 74xxx-Serie um 15 ns und bestimmt direkt die maximale Arbeitsfrequenz und die Geschwindigkeit der Datenverarbeitung dieser Schaltkreise.